3.1 Early Vector Supercomputers

The first era of commercially successful parallel computing was significantly influenced by the work of Seymour Cray. His name became associated with supercomputing, and his design philosophy influenced high-performance computing for nearly two decades.

The Architect: Seymour Cray

Section titled “The Architect: Seymour Cray”Seymour Cray’s career began at Control Data Corporation (CDC), where he established his reputation as an architect of high-speed computers.1 His designs, like the CDC 1604 and the CDC 6600, were the fastest of their time.2 The CDC 6600, released in 1964, is widely considered the first supercomputer.1

Cray’s design philosophy focused on performance, achieved through minimalist designs that utilized the fastest available components.

He left CDC in 1972 to found Cray Research, a company focused on building high-performance computers.2

Case Study: The CDC STAR-100

Section titled “Case Study: The CDC STAR-100”Before Cray Research released its first system, other companies had attempted to utilize vector processing. The concept was to perform a single operation on an entire array (“vector”) of numbers at once.2 The CDC STAR-100, first delivered in 1974, was the world’s first commercially available vector supercomputer.3 Designed by James Thornton at Control Data Corporation, it was engineered specifically for Lawrence Livermore National Laboratory’s nuclear physics simulations.3

Architectural Characteristics

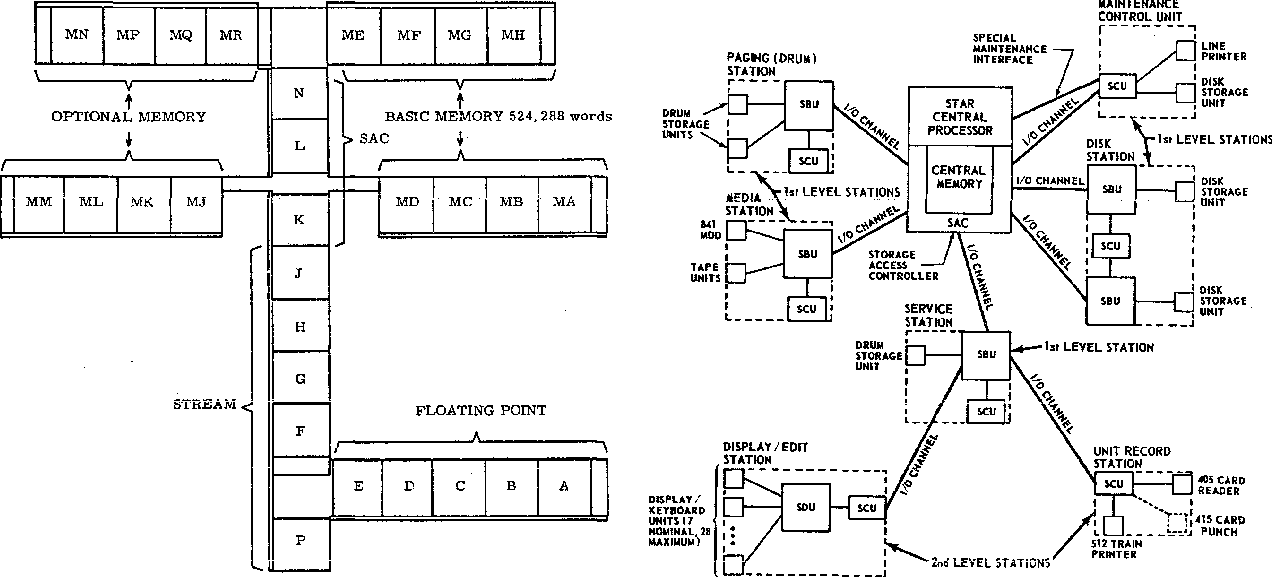

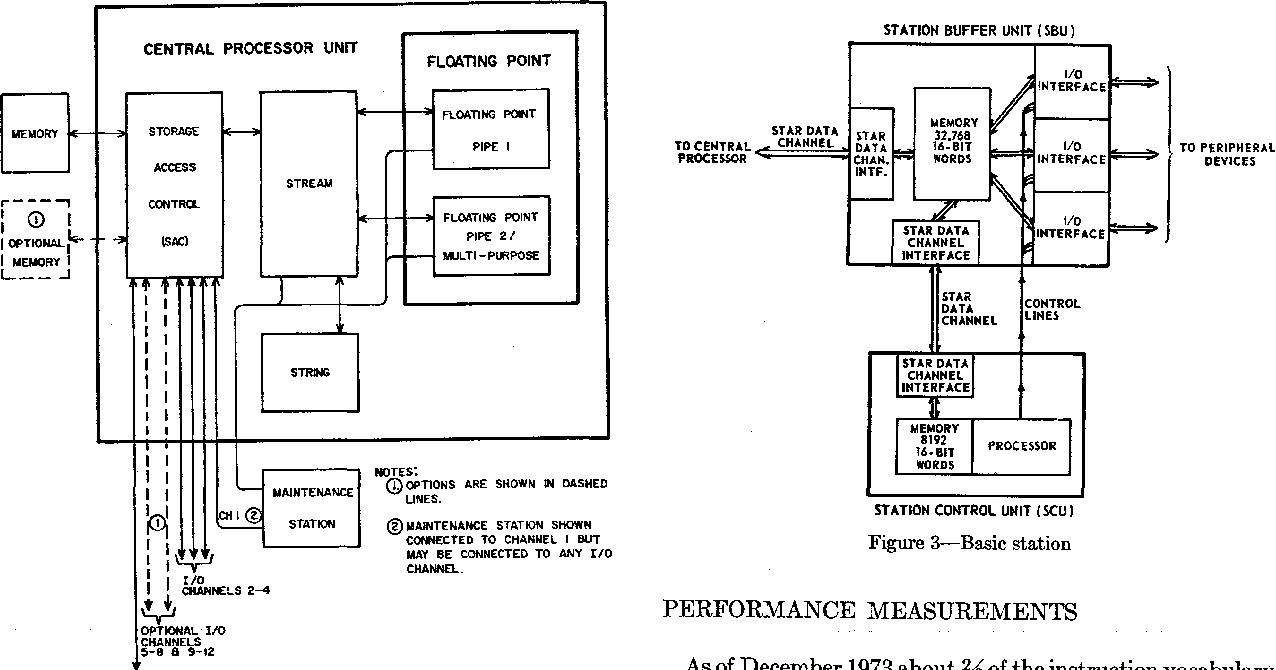

Section titled “Architectural Characteristics”The STAR-100 operated at 25 MHz (40 nanosecond cycle time) and introduced several pioneering features:3

- 512-Bit “Superword” Architecture: Memory transferred data in 512-bit units (eight 64-bit floating-point numbers simultaneously), providing high bandwidth for vector operations.3

- Deeply Pipelined Arithmetic Units: Two independent segmented pipelines handled floating-point operations, with Pipeline 2 also managing all scalar instructions.3

- Virtual Memory: The STAR-100 was the first supercomputer to implement virtual memory, using a 48-bit address space with page sizes of 512 words or 65,536 words.3

- Distributed I/O Architecture: The system employed satellite “Stations” based on CDC 1700 minicomputers to handle I/O operations, preventing the central processor from being slowed by peripheral devices.3

| Architecture Type | Memory-to-Memory (e.g., CDC STAR-100) |

|---|---|

| Concept | Vector instructions stream data directly from main memory, through the arithmetic units, and back to memory.4 |

| Peak Performance | 100 MFLOPS (64-bit), 200 MFLOPS (32-bit split-pipe mode)3 |

| Strength | High bandwidth for long, sequential data vectors. |

| Limitations | 1. High Startup Overhead: Vector breakeven point often exceeded 100 elements.5 2. Poor Scalar Performance: Slow scalar unit due to deep pipeline latency.43 3. Memory Dependency: Performance bottlenecked by memory access patterns.3 |

| Outcome | Often performed worse than contemporary scalar machines on real-world scientific programs, which are a mix of vector and scalar work.4 |

These early machines demonstrated the importance of balanced performance; a supercomputer must perform well on both scalar and vector operations.5

The Cray-1 Architecture (1976)

Section titled “The Cray-1 Architecture (1976)”In 1976, Cray Research released the Cray-1.2 It was a balanced architecture that addressed the limitations of earlier vector machines.

The design reflected the principle later formalized as Amdahl’s Law: the speedup of a program is ultimately limited by its sequential, non-parallelizable fraction.7

The Cray-1’s design was a balanced architecture, ensuring efficient performance on the scalar portions of a program.

Key Architectural Innovations:

Section titled “Key Architectural Innovations:”The Cray-1 operated with a 12.5 nanosecond clock period (80 MHz), achieving 160 MFLOPS peak performance.8 Its architecture featured several critical innovations:

- High-Speed Scalar Unit: The Cray-1 included one of the fastest scalar processors of its time, with a scalar/vector crossover point of only 2-4 elements (compared to 100+ for the STAR-100).8 This ensured high performance on the non-vectorizable parts of any code.4

- Register Hierarchy: The architecture employed five register sets:8

- Eight 64-bit S (Scalar) registers for computational operands

- Eight 24-bit A (Address) registers for memory addressing and loop control

- Eight 64-element V (Vector) registers for vector operations

- Sixty-four 64-bit T registers and sixty-four 24-bit B registers for intermediate buffering

- Register-to-Register Architecture: Instead of streaming from main memory, data was loaded into high-speed vector registers, operated on, and written back. This significantly reduced memory traffic.59

- Twelve Segmented Functional Units: All units could operate concurrently, with varying latencies (2-14 clock periods depending on operation).8 The Reciprocal Approximation Unit enabled pipelined division through iterative methods.8

- 16-Way Memory Interleaving: Main memory was organized into 16 independent banks to prevent bank conflicts and sustain one-word-per-cycle throughput.8

- Vector Chaining: This breakthrough feature allowed results from one functional unit to be directly forwarded to another, creating customized deep pipelines without intermediate memory access.298 This enabled sustained performance approaching theoretical peak (138 MFLOPS sustained, with bursts up to 250 MFLOPS).8

| Feature | CDC STAR-100 | Cray-1 |

|---|---|---|

| Architecture | Memory-to-Memory | Register-to-Register |

| Clock Speed | 25 MHz (40 ns cycle) | 80 MHz (12.5 ns cycle) |

| Vector Data | Streamed from Main Memory (512-bit units) | Held in 8 Vector Registers (64 elements each) |

| Memory System | 32-way interleaved magnetic core | 16-way interleaved bipolar semiconductor |

| Scalar Speed | Poor (deep pipeline latency) | Excellent (fastest of its era) |

| Vector Breakeven | 100+ elements | 2-4 elements |

| Pipelining | Two deep pipelines | Twelve segmented functional units with chaining |

| Peak Performance | 100 MFLOPS (64-bit), 200 MFLOPS (32-bit) | 160 MFLOPS peak, 138 MFLOPS sustained |

| Virtual Memory | Yes (48-bit address space) | No (physical addressing only) |

Physical Design and Engineering

Section titled “Physical Design and Engineering”The physical design of the Cray-1 was as notable as its internal architecture. Every aspect of its physical form was a solution to an engineering challenge.

- C-Shaped Chassis: This shape was a solution to signal propagation delays.10 To achieve a clock cycle of 12.5 nanoseconds, all wires had to be extremely short. The cylindrical design (8.5 feet wide, 6.5 feet high) minimized the maximum wire length, with 60 miles of internal wiring controlled by strict length rules (multiples of 1 foot, maximum 4 feet).11128

- Dense, High-Speed Logic: The system was built with 95% of its logic using a single type of custom integrated circuit, providing standardization and reliability.138 This density generated four times the heat per cubic inch compared to the CDC 7600.8

- Freon Cooling System: To dissipate the 115 kW of heat, a novel Freon-based cooling system was developed. Vertical aluminum/stainless steel cooling bars in each column wall conducted heat to a refrigeration unit in the surrounding bench.108

- Reliability: System availability exceeded 98% with mean time between interruption (MTBI) over 100 hours, demonstrating the quality of the engineering.8

| Cray-1 Specification | Value |

|---|---|

| Clock Speed | 80 MHz (12.5 ns cycle time) |

| Peak Performance | 160 MFLOPS |

| Memory | Up to 1 million 64-bit words |

| Power Consumption | 115 kW |

| Cost | 8 million USD 5 |

Impact and Legacy

Section titled “Impact and Legacy”The Cray-1 was a commercial success, with over 80 systems sold.5 It became an important tool for national laboratories and research universities, enabling research in:

- Nuclear weapons simulation

- Cryptography

- Weather forecasting

- Computational fluid dynamics1

Its successors, the Cray X-MP and Y-MP, introduced shared-memory multiprocessing, allowing multiple vector processors to work in parallel on a single problem and increasing performance into the gigaflops range.1 For more than a decade, Seymour Cray’s design philosophy represented high-performance computing, creating a legacy of custom, high-performance, and balanced architectural design.

References

Section titled “References”Footnotes

Section titled “Footnotes”-

Cray-1 | computer - Britannica, accessed October 2, 2025, https://www.britannica.com/topic/Cray-1 ↩ ↩2 ↩3 ↩4

-

History of supercomputing - Wikipedia, accessed October 2, 2025, https://en.wikipedia.org/wiki/History_of_supercomputing ↩ ↩2 ↩3 ↩4 ↩5

-

CDC STAR-100 - Wikipedia, accessed November 18, 2025, https://en.wikipedia.org/wiki/CDC_STAR-100 ↩ ↩2 ↩3 ↩4 ↩5 ↩6 ↩7 ↩8 ↩9 ↩10

-

Vector Architectures: Past, Present and Future, accessed October 2, 2025, https://www.cs.cmu.edu/afs/cs/academic/class/15740-f03/public/doc/discussions/uniprocessors/vector/vector-past-present-future-supercomputing98.pdf ↩ ↩2 ↩3 ↩4

-

Cray-1 - Wikipedia, accessed October 2, 2025, https://en.wikipedia.org/wiki/Cray-1 ↩ ↩2 ↩3 ↩4 ↩5

-

The control data STAR-IOO-Performance measurements, accessed October 16, 2025, https://api.semanticscholar.org/CorpusID:43509695 ↩ ↩2

-

History of computer clusters - Wikipedia, accessed October 2, 2025, https://en.wikipedia.org/wiki/History_of_computer_clusters ↩

-

The CRAY- 1 Computer System - cs.wisc.edu, accessed November 18, 2025, https://pages.cs.wisc.edu/~markhill/restricted/cacm78_cray1.pdf ↩ ↩2 ↩3 ↩4 ↩5 ↩6 ↩7 ↩8 ↩9 ↩10 ↩11 ↩12 ↩13

-

I INM MoRY J - Cray simulator, accessed October 2, 2025, https://cray.modularcircuits.com/cray_docs/articles/an_analysis_of_the_cray1_computer.PDF ↩ ↩2

-

The CRAY-1 Computer System^, accessed October 2, 2025, https://tcm.computerhistory.org/ComputerTimeline/Chap44_cray1_CS2.pdf ↩ ↩2

-

The Cray-1 Computer System, 1977, accessed October 2, 2025, https://s3data.computerhistory.org/brochures/cray.cray1.1977.102638650.pdf ↩

-

The Cray-1 Supercomputer - CHM Revolution - Computer History Museum, accessed October 2, 2025, https://www.computerhistory.org/revolution/supercomputers/10/7 ↩

-

The CRAY- 1 Computer System, accessed October 2, 2025, https://www.cs.auckland.ac.nz/courses/compsci703s1c/archive/2008/resources/Russell.pdf ↩